FASTER | HARDWARE

FASTER hardware is divided in two parts

MOTHER BOARDS

DAUGHTER BOARDS

There are two motherboards available. You can use FASTER on a microTCA crate (syroco_amc_c5), or directly on a table (syroco_c5). The functions of the mother boards are to provide :

- VITA-57 slot(s),

- FPGA (s),

- a master clock,

- a T0 signal,

- network connection(s)

The function of the daughter boards is to provide a interface between the detector and the FPGA. Currently, four daughter boards have been developed.

CARAS provides users a dual channel 12-bits up to 500 Msps ADC capability, ideally suited for time of flight, charge, RF and energy measurement.

MOSAHR provides users a four channel 14-bits up to 125 Msps ADC capability, ideally suited for high resolution energy measurement.

CARAMEL provides 32 low input current integrator channels for ionization chamber or photodiode detectors

HV board is capable of supplying stabilized high voltage from ±500 V to ±6 kV (4W).

A new daughter-board is under development with a dual channel 16 bits up to 500 Msps ADC device.

MOTHER BOARDS

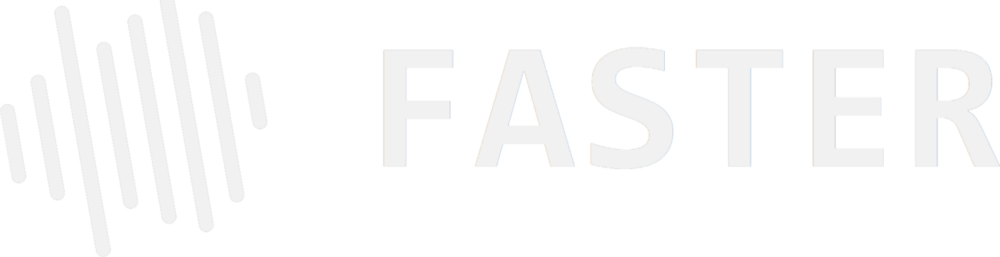

SYROCO_AMC_C5 is used for large experiment. All the boards inside the same microTCA crate are synchronized together.

Key Features

- 2 VITA 57 slots,

- 3 Cyclone5 FPGAs from ALTERA (5CGTFD7C3F23C7N),

- 1 and 10 Gbe connection,

- Synchronize by a external clock,

- FPGA firmware downloading by Ethernet.

SYROCO_C5 is the last version (new FPGA) of our smallest mother board of the project (Useful for developments or small detector tests).

Key Features

- 1 VITA 57 slot,

- 1 Cyclone5 FPGA from ALTERA (5CGTFD7C3F23C7N),

- 1 Gbe connection,

- FPGA firmware downloading by Ethernet.

SYROCO_V2 is the smallest mother board of the project (Useful for developments or small detector tests).

Key Features

- 1 VITA 57 slot,

- 1 Cyclone3 FPGA from ALTERA (EP3C40F484C6N),

- 1 Gbps Ethernet connection,

- Program the FPGA’s firmare by the jtag connector or over Ethernet network.

SYROCO_AMC is used for large experiment. All the boards inside the same microTCA crate are synchronized together.

Key Features

- 2 VITA 57 slots,

- 2 Cyclone3 FPGAs from ALTERA (EP3C40F484C6N),

- 1 ARRIA1GX FPGA from ALTERA (EP1AGX35CF484C6N),

- 1 Ethernet connection,

- 10 Gigabits connection (Not available for the moment)

- Synchronize by a external clock,

- Program the FPGA’s firmare over Ethernet network.

DAUGHTER BOARDS

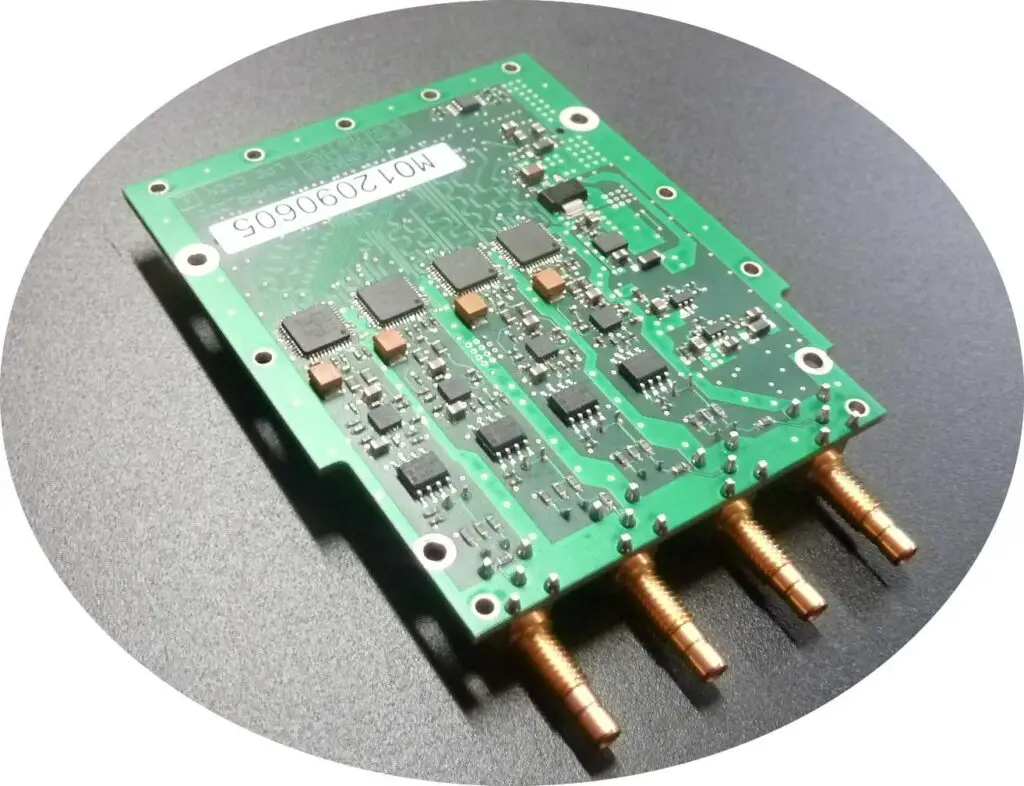

CARAMEL (CARte Acquisition Multivoies ELextromètre)

CARAMEL is the third daughter card for the FASTER project. The 32 channels synchronous current input ADC has been developed on this card.

Key Features

- VITA57 format

- 32 channels (16 Bits 20 µs or 12 Bits 10µs)

- Integrating I-To-V conversion front-end,

- Programmable full-scale : 3pC to 12 pC

- Adjustable integration times range from 10μs to 1ms

- Applications (Ionization chamber, MWPC, Photodiode sensors)

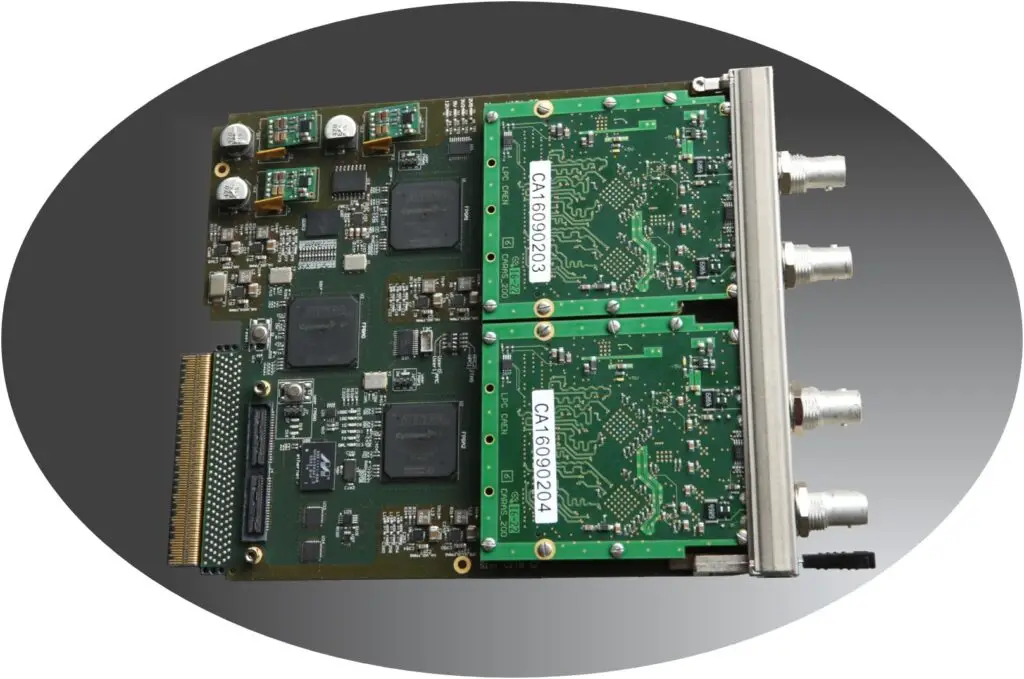

MOSAHR

MOSAHR is the second daughter card developed for the FASTER project. The ADC module for high spectroscopy measurement has been developed for this card. Key Features- VITA57 format

- 4 channels = 4 FADC (125MHz, 14 Bits)

- ±1V, ±2V, ±5V, ±10V input dynamic range on 10kΩ (switch selection)

| S1 | S2 | INPUT RANGE | INPUT IMPEDANCE |

| ON | ON | ± 5 V | 2 kΩ |

| ON | OFF | ± 1V | 3 kΩ |

| OFF | ON | ± 10V | 4 kΩ |

| OFF | OFF | ± 2V | 5 kΩ |

- Noise: 1 lsbrms ≈ 130μVrms (±1V range)

- Bandwidth = 25 MHz

- Crosstalk isolation › 97 DB

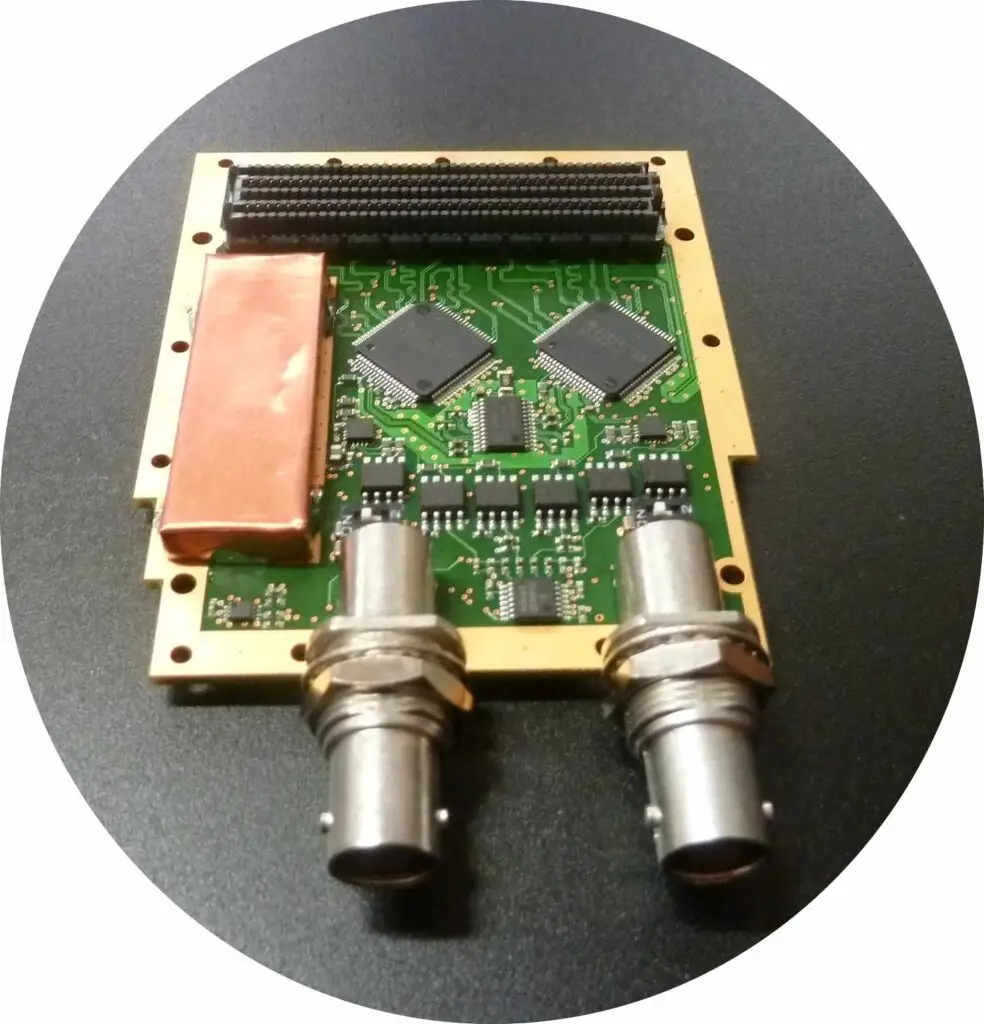

CARAS

CARAS is the first daughter card developed for the FASTER project. The QDC-TDC, RF and ADC modules have been developed for this card. You can easily change the function by reprogramming the FPGA on the mother card. Key Features- VITA57 format

- 2 channels = 2 FADC (500MHz, 12 Bits)

- ±1.15V dynamic range (50Ω or 10kΩ) (switch selection)

| S1 | S2 | INPUT IMPEDANCE |

| ON | ON | 50 Ω |

| OFF | OFF | 10 kΩ |

- Input Offset ajustable by software between -1.1V and 1.1V

- Noise: 1.1lsbrms ≈ 600μVrms

- Bandwidth = 100 MHz

ADDRESS

LPC CAEN

6 Bd Maréchal Juin

14050 CAEN CEDEX

PHONE

(+33) 2 31 45 25 00